# Module Control of the jFEX for the ATLAS Calorimeter Trigger Upgrade

by

### **Rouven Spreckels**

n3vu0r@qu1x.org

**Diploma Thesis in Physics**

3rd June 2016

Supervisor

Prof. Dr. Stefan Tapprogge

## Abstract

The ATLAS experiment at the Large Hadron Collider (LHC) is a generalpurpose particle detector searching for new fundamental physics discoveries. The LHC and the ATLAS detector will be upgraded to reach higher luminosities and finer granularities, respectively. To maintain trigger efficiency, new subsystems will be installed as part of the upgrade, such as the Jet Feature Extractor (jFEX). It will identify in real-time jets and  $\tau$  particles and calculate energy sums with the data received from electromagnetic and hadronic calorimeters by running its algorithms on multiple processor FPGAs. The implementations and configurations of these algorithms are provided by a single control FPGA accessed through a central control interface. For reasons of flexibility, this control FPGA is placed on a mezzanine card based on a hybrid system on a chip (SoC), combining an FPGA and a CPU inside a single chip with many interconnects in between. This thesis presents the design of this mezzanine card and the software developed to demonstrate use cases of the hybrid SoC approach.

## **Statutory Declaration**

I hereby confirm that I have written the present thesis independently and without illicit assistance from third parties and using solely the aids mentioned.

Mainz, 3rd June 2016

**Rouven Spreckels**

## Contents

| 1 | Ove  | verview 9                          |    |  |

|---|------|------------------------------------|----|--|

| 2 | Intr | roduction 1                        | 1  |  |

|   | 2.1  | Large Hadron Collider 1            | 1  |  |

|   | 2.2  | ATLAS Experiment                   | 13 |  |

|   |      | 2.2.1 Detector                     | 13 |  |

|   |      | 2.2.2 Trigger and Data Acquisition | 4  |  |

|   |      | 2.2.3 Calorimeter Trigger          | 15 |  |

|   |      | 2.2.4 Calorimeter Trigger Upgrade  | L7 |  |

|   | 2.3  | Jet Feature Extractor              | 18 |  |

| 3 | Har  | rdware Design 2                    | 21 |  |

|   | 3.1  | Design Specification               | 21 |  |

|   |      | 3.1.1 Central Control Interface    | 22 |  |

|   |      | 3.1.2 Intra-Board Communication    | 23 |  |

|   |      | 3.1.3 Debugging Facilities         | 24 |  |

|   | 3.2  | Conceptual Design                  | 24 |  |

|   | 3.3  | First Iteration                    | 28 |  |

| 4 | Sof  | tware Development 3                | 81 |  |

|   | 4.1  | Workflow Kit                       | 32 |  |

|   |      | 4.1.1 Dependency Resolution        | 32 |  |

|   |      | 4.1.2 Modification Management      | 34 |  |

|   |                                               | 4.1.3                                                                    | Development Process                                                                                                                                                                                                                                                                                                        | 36                                           |

|---|-----------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|   |                                               | 4.1.4                                                                    | Toolchain Encapsulation                                                                                                                                                                                                                                                                                                    | 37                                           |

|   | 4.2                                           | CPU/                                                                     | FPGA Communication                                                                                                                                                                                                                                                                                                         | 38                                           |

|   |                                               | 4.2.1                                                                    | Communication Protocol                                                                                                                                                                                                                                                                                                     | 39                                           |

|   |                                               | 4.2.2                                                                    | Memory Mapping                                                                                                                                                                                                                                                                                                             | <b>1</b> 1                                   |

|   |                                               | 4.2.3                                                                    | Master Implementation                                                                                                                                                                                                                                                                                                      | 17                                           |

|   |                                               | 4.2.4                                                                    | Slave Implementation                                                                                                                                                                                                                                                                                                       | 50                                           |

|   |                                               | 4.2.5                                                                    | File Transfer Application 5                                                                                                                                                                                                                                                                                                | 53                                           |

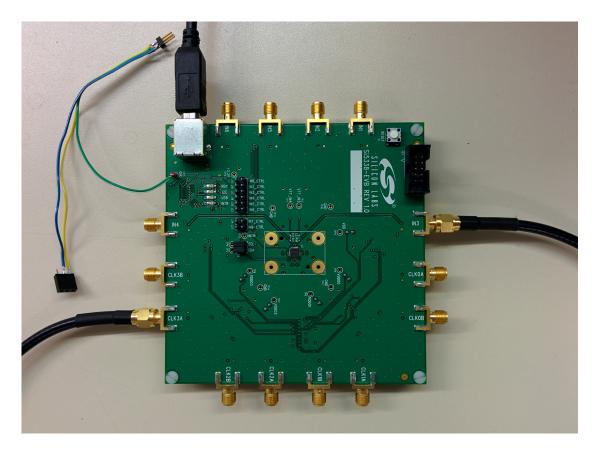

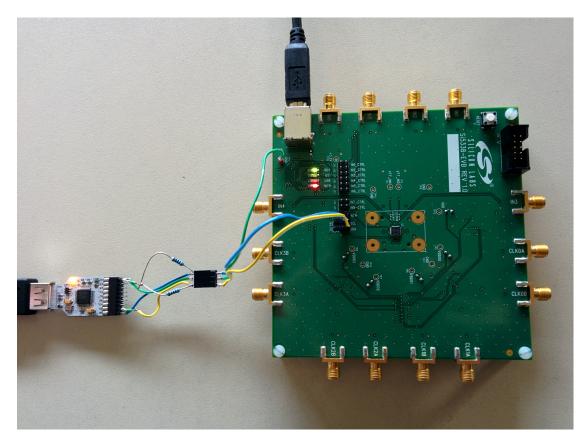

|   | 4.3                                           | Clock                                                                    | Generation                                                                                                                                                                                                                                                                                                                 | 56                                           |

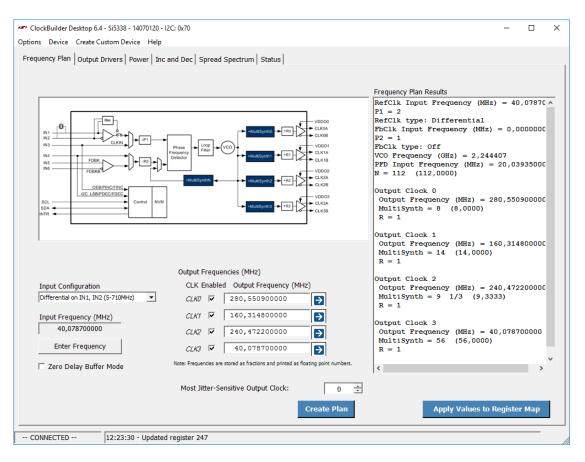

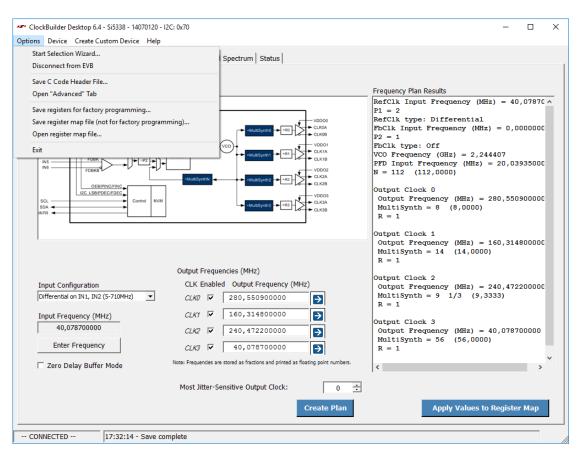

|   |                                               | 4.3.1                                                                    | Register Map Creation                                                                                                                                                                                                                                                                                                      | 57                                           |

|   |                                               | 4.3.2                                                                    | Register Map Conversion                                                                                                                                                                                                                                                                                                    | 34                                           |

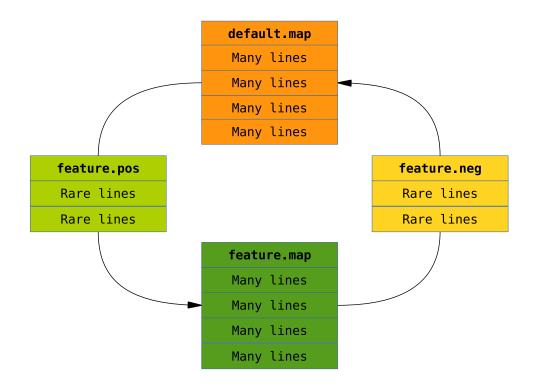

|   |                                               | 4.3.3                                                                    | Transition Map Generation                                                                                                                                                                                                                                                                                                  | <b>5</b> 8                                   |

|   |                                               |                                                                          |                                                                                                                                                                                                                                                                                                                            |                                              |

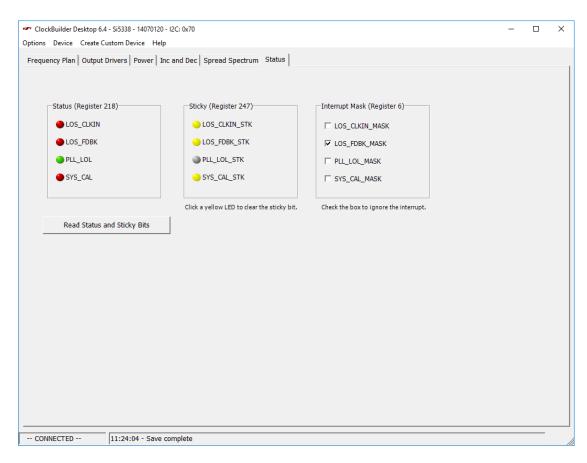

|   |                                               | 4.3.4                                                                    | Device Control                                                                                                                                                                                                                                                                                                             | 73                                           |

| 5 | Test                                          | 4.3.4<br>ts & R                                                          |                                                                                                                                                                                                                                                                                                                            | 73<br>7 <b>7</b>                             |

| 5 | <b>Tes</b><br>5.1                             | ts & R                                                                   | esults 7                                                                                                                                                                                                                                                                                                                   |                                              |

| 5 |                                               | ts & R<br>Bootin                                                         | esults 7                                                                                                                                                                                                                                                                                                                   | <b>77</b><br>77                              |

| 5 | 5.1                                           | ts & R<br>Bootin                                                         | esults 7<br>ng the Operating System                                                                                                                                                                                                                                                                                        | 77<br>77<br>33                               |

| 5 | 5.1                                           | ts & R<br>Bootin<br>Testir                                               | esults 7<br>ng the Operating System                                                                                                                                                                                                                                                                                        | 77<br>77<br>33<br>34                         |

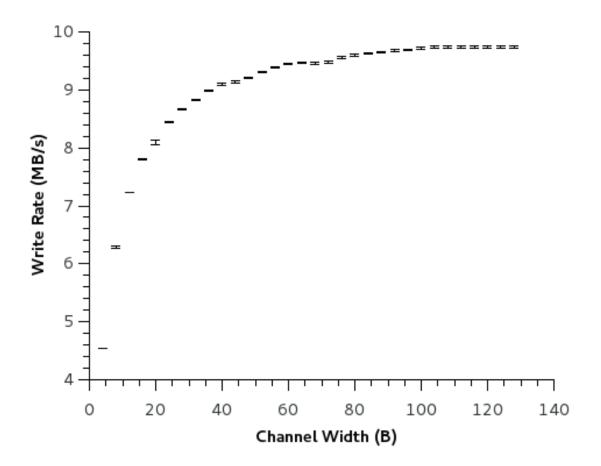

| 5 | 5.1                                           | ts & R<br>Bootin<br>Testir<br>5.2.1                                      | esults       7         ng the Operating System       7         ng the CPU/FPGA Communication       8         Data Integrity Verification       8         Write Rate Measuring       8                                                                                                                                      | 77<br>77<br>33<br>34                         |

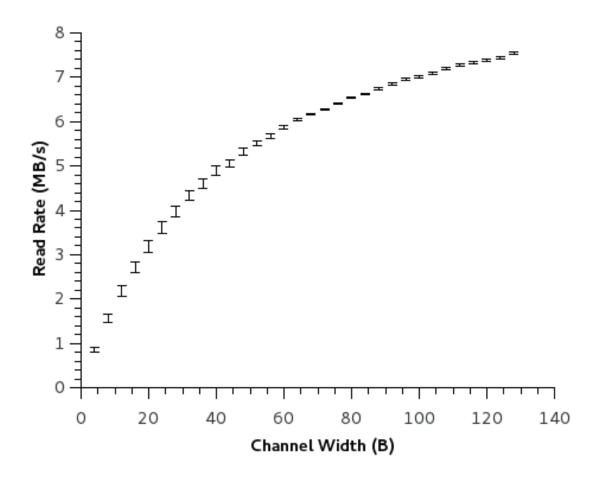

| 5 | 5.1                                           | ts & R<br>Bootin<br>Testir<br>5.2.1<br>5.2.2<br>5.2.3                    | esults 7 ng the Operating System                                                                                                                                                                                                                                                                                           | 77<br>77<br>33<br>34<br>36<br>90             |

| 5 | 5.1<br>5.2                                    | ts & R<br>Bootin<br>Testin<br>5.2.1<br>5.2.2<br>5.2.3<br>Testin          | esults       7         ng the Operating System                                                                                                                                                                                                                                                                             | 77<br>77<br>33<br>34<br>36<br>90             |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | ts & R<br>Bootin<br>Testin<br>5.2.1<br>5.2.2<br>5.2.3<br>Testin          | esults       7         ng the Operating System       7         ng the CPU/FPGA Communication       8         Data Integrity Verification       8         Write Rate Measuring       8         Read Rate Measuring       9         ng the I <sup>2</sup> C Communication       9         olling the Clock Generator       9 | 77<br>77<br>33<br>34<br>36<br>90             |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | ts & R<br>Bootin<br>Testin<br>5.2.1<br>5.2.2<br>5.2.3<br>Testin<br>Contr | esults       7         ng the Operating System       7         ng the CPU/FPGA Communication       8         Data Integrity Verification       8         Write Rate Measuring       8         Read Rate Measuring       9         ng the I <sup>2</sup> C Communication       9         olling the Clock Generator       9 | 77<br>33<br>34<br>36<br>90<br>94<br>97<br>98 |

#### 6 Conclusion & Outlook

109

### Chapter 1

### **Overview**

The ATLAS experiment [1] at the Large Hadron Collider (LHC) [2] is a generalpurpose particle detector searching for new fundamental physics discoveries while further investigating the properties of its recent discoveries [3], whether predicted by the Standard Model or beyond of it. To study elementary particles and their fundamental interactions, they are accelerated to high kinetic energies in order to let them collide and to analyze their products. The ATLAS detector [1] generates data for each detected event resulting in such high data rates, unmanageable to be stored for long-term analyzes. Thus, a trigger system [4] is used to select in real-time the rare interesting events giving hints to new physics, reducing the effective data rates down to a manageable level. In order to make trigger decisions in real-time, custom-made electronics are used to meet the necessary discriminatory power. The LHC and the ATLAS detector were and will further be upgraded to reach higher luminosities and finer granularities, respectively [5]. Thus, the trigger system was and will further be upgraded as well to manage the increased data rates generated by the detector. The trigger system is divided into calorimeter and muon triggers. The Jet Feature Extractor (*jFEX*) [6] currently being designed will augment the modules of the present calorimeter trigger as part of the next upgrade to meet the need for more discriminatory power. It will identify in real-time jets and  $\tau$  particles and calculate energy sums with the data received from the electromagnetic and hadronic calorimeters of the detector by running its algorithms on multiple FPGAs, here referred to as processor FPGAs. The implementations and configurations of these algorithms are provided by a single control FPGA accessed through a central control interface. For reasons of flexibility, this control FPGA is placed on a daughter module, a so-called mezzanine card. This mezzanine card further controls several subcomponents of the jFEX. It populates a hybrid system on a chip (SoC),

combining an FPGA and a CPU inside a single chip with many interconnects in between. The following chapter 2 introduces the jFEX while describing its integration into the ATLAS experiment at the LHC. I have collaborated on the hardware design of the mezzanine card which is presented in chapter 3, while chapter 4 covers the software I have developed to demonstrate use cases of the hybrid SoC approach regarding the module control of the jFEX. Finally, I have tested the mezzanine card in combination with the developed software as described in chapter 5, followed by a conclusion and outlook in chapter 6.

## **Chapter 2**

## Introduction

The Standard Model of particle physics has successfully explained and predicted many experimental results like the discovery of the Higgs boson in 2012 [3]. But for beyond of what this theory is capable to explain like dark matter particles, ongoing research is necessary to further develop its description of elementary particles and their fundamental interactions. To study their laws of nature, particles are accelerated to high kinetic energies in order to let them collide and to analyze their products. Many interesting particles are only produced at high collision energies. The challenge is to select the rare interesting events giving hints to new physics.

### 2.1 Large Hadron Collider

The Large Hadron Collider (LHC) [2] is located at the European Organization for Nuclear Research (CERN)<sup>1</sup> near Geneva, Switzerland. As of writing time, it is the world's largest and most powerful particle collider, lying 100 meters beneath ground in a tunnel of 27 kilometers in circumference. It accelerates hadrons, specifically protons or lead ions, in two adjacent parallel beam pipes of opposite directions. These pipes intersect at four points allowing the beams to collide within the de-

<sup>&</sup>lt;sup>1</sup> The original "Conseil Européen pour la Recherche Nucléaire" (CERN) was dissolved [7].

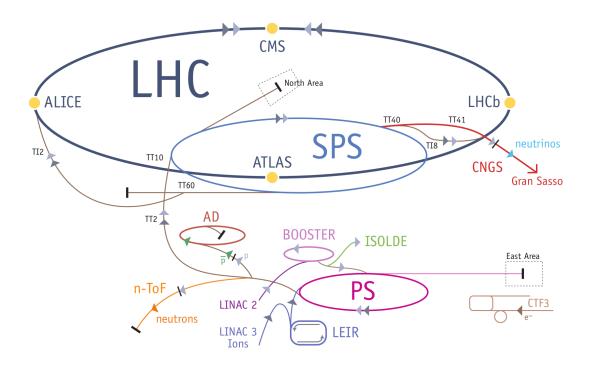

tectors of the four main experiments ATLAS<sup>2</sup>, CMS<sup>3</sup>, ALICE<sup>4</sup>, and LHCb<sup>5</sup> each located at an intersection point, as shown in figure 2.1. First two are general-purpose particle detectors while last two are more specialized ones.

Figure 2.1: LHC Overview [2]

The beam parameters of the operational runs of proton-proton collisions are shown in table 2.1, which are the center-of-mass energy  $\sqrt{s}$ , the instantaneous luminosity<sup>6</sup> L, and the average number of interactions per bunch-crossing  $\langle \mu \rangle$  along with its peak value  $\mu_{max}$ . A long shutdown between the runs is used to install upgrades in order to reach the increased parameters.

$<sup>^{2}</sup>$  A Toroidal LHC ApparatuS (ATLAS) is a general-purpose detector experiment [2].

<sup>&</sup>lt;sup>3</sup> The Compact Muon Solenoid (CMS) is a general-purpose detector experiment [2].

<sup>&</sup>lt;sup>4</sup> A Large Ion Collider Experiment (ALICE) is a specialized detector for heavy ions [2].

<sup>&</sup>lt;sup>5</sup> The LHC beauty (LHCb) experiment is a specialized detector for B mesons [2].

<sup>&</sup>lt;sup>6</sup> The luminosity  $L = \frac{1}{\sigma} \frac{dN}{dt}$  is the rate of events produced per second  $\frac{dN}{dt}$  and cross-section  $\sigma$ .

| Run                                          | Years     | $\sqrt{s}$ (TeV) | $L (10^{34} \mathrm{cm}^{-2} \mathrm{s}^{-1})$ | $\langle \mu \rangle$ | $\mu_{max}$ |  |

|----------------------------------------------|-----------|------------------|------------------------------------------------|-----------------------|-------------|--|

| 1                                            | 2010-2012 | $\leq 8$         | 0.77                                           | 21                    | 36          |  |

| Phase-0 Upgrade during Long Shutdown 1 (LS1) |           |                  |                                                |                       |             |  |

| 2                                            | 2015-2017 | 13               | $\sim 1.6$                                     | 40                    | $\sim 60$   |  |

| Phase-1 Upgrade during Long Shutdown 2 (LS2) |           |                  |                                                |                       |             |  |

| 3                                            | 2020-2022 | 13               | $\sim 2.5$                                     | 60                    | $\sim 80$   |  |

| Phase-2 Upgrade during Long Shutdown 3 (LS3) |           |                  |                                                |                       |             |  |

| 4                                            | 2025-2027 | 14               | $\sim 5.0$                                     | 140                   | $\sim 200$  |  |

Table 2.1: LHC Evolution [5]

### 2.2 ATLAS Experiment

The goals of the ATLAS experiment are to search for new discoveries and further investigate its recent discoveries like the properties of the Higgs boson [1]. Ongoing measurements will allow in-depth analyzes of the Standard Model and beyond of it.

#### 2.2.1 Detector

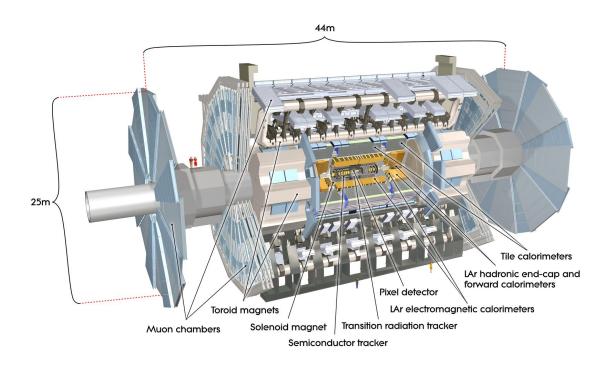

The ATLAS detector [1] shown in figure 2.2 is composed of concentric cylinders surrounding an intersection point of the LHC where the proton beams collide. Its main components are the inner detector, the inner electromagnetic calorimeter (ECAL), the outer hadronic calorimeter (HCAL), and the outermost muon spectrometer. Each is specialized to detect certain types and properties of particles, complementing to a general-purpose detector in a whole by covering various particles with a broad range of energies.

Figure 2.2: ATLAS Detector [1]

The inner detector is the closest to the proton beam with a gap of only a few centimeters. It tracks charged particles in order to reconstruct their trajectories. Due to a magnetic field within the inner detector, these trajectories are curved. Their direction and degree of curvature reveals the sign of the charge and the momentum of a particle, respectively. The two calorimeters measure energy absorptions of particle showers caused by interactions with their material. The initial energy of particles is inferred by sampling their showers. The inner calorimeter covers electromagnetic interactions and the outer calorimeter covers strong interactions. The muon spectrometer functions similarly to the inner detector by curving the trajectories of muons with a magnetic field in order to measure their momentum.

#### 2.2.2 Trigger and Data Acquisition

According to the Technical Design Report (TDR) for the Phase-1 upgrade of the AT-LAS Trigger and Data Acquisition (TDAQ) system [4], the LHC collides two bunches of protons every 25 ns resulting in 40 million bunch-crossings in a second, that is a bunch-crossing rate of 40 MHz. For each bunch-crossing the data generated by the several sub-detectors sum up to about 2.4 MB after zero suppression. This results in an unmanageable data rate of roughly  $40 \text{ MHz} \cdot 2.4 \text{ MB} = 96 \text{ TB/s}$ . Since not all

events are interesting, a pipelined trigger system of multiple stages is used to select in real-time the potentially interesting events and their regions of interest (RoIs) within the detector. This reduces the effective event rate and its corresponding data rate step by step down to a manageable level of roughly  $2.4 \,\mathrm{GB/s}$  to be stored for long-term analyzes, as shown in table 2.2.

| Stage               | Trigger Rate      | Data Rate          |

|---------------------|-------------------|--------------------|

| Detector Read-Out   | $40\mathrm{MHz}$  | $96\mathrm{TB/s}$  |

| Level-1 Accepts     | $100\mathrm{kHz}$ | $240\mathrm{GB/s}$ |

| High-Level Requests | $40\mathrm{kHz}$  | $60\mathrm{GB/s}$  |

| Event Building      | $12\mathrm{kHz}$  | $29\mathrm{GB/s}$  |

| Event Filtering     | 1 kHz             | $2.4\mathrm{GB/s}$ |

Table 2.2: Trigger & Data Rates during Run 2 [4]

The trigger system is divided into two levels of event selection, the Level-1 (L1) and the High-Level Trigger (HLT). The L1 is implemented using custom-made electronics based on ASICs<sup>7</sup> and FPGAs<sup>8</sup> while the HLT is based on farms of commercially available computers and networking hardware. Each stage of table 2.2 reduces the effective event rate giving the algorithms of the next stage respectively more time to analyze the data with more complex algorithms and more precise selection criteria. The L1 trigger, divided into calorimeter trigger (L1Calo) and muon trigger (L1Muon), has less than  $2.5 \,\mu$ s per bunch-crossing to make its decisions and to transfer its results to the HLT while it is concurrently fed by the data stream of the current bunch-crossing due to being a pipelined system.

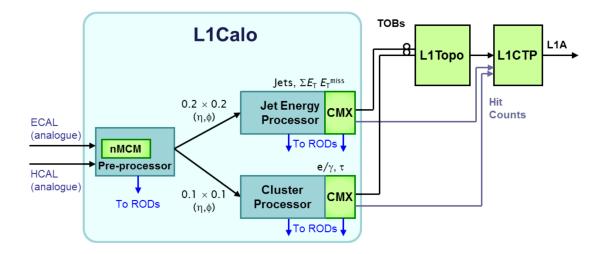

#### 2.2.3 Calorimeter Trigger

The Level-1 Calorimeter Trigger (L1Calo) currently being used during Run 2, that is after the Phase-0 upgrade [4], identifies  $e/\gamma$  and  $\tau$  particles<sup>9</sup> with the data received from the ECAL and HCAL. Furthermore, it identifies jets and events of large missing transverse energy  $E_T^{miss}$  (XE) along with its significance XS, and large total transverse energy  $\sum E_T$  (TE). The architecture of the L1Calo system is shown in figure 2.3.

<sup>&</sup>lt;sup>7</sup> An application-specific integrated circuit (ASIC) is an IC manufactured for a custom use.

<sup>&</sup>lt;sup>8</sup> A field-programmable gate array (FPGA) is an IC customizable after manufacturing.

$<sup>^9</sup>$  Not distinguishing between  $e^-,\,e^+,$  and  $\gamma$  while only identifying hadronically decaying  $\tau.$

Figure 2.3: L1Calo System Architecture during Run 2 [4]

The L1Calo system receives analogue signals from the ECAL and HCAL. The Pre-Processor Modules (PPMs) digitize them with a sampling rate of 80 MHz and send them to the Cluster Processor (CP) subsystem and to the Jet Energy Processor (JEP) subsystem. Each subsystem consists of multiple modules, 56 Cluster Processor Modules (CPMs) and 32 Jet Energy Processor Modules (JEMs), respectively. They are installed in a crate and connected through its backplane. Each CPM identifies and counts energy deposits indicative of isolated  $e/\gamma$  and  $\tau$  particles within a given area of the calorimeter data while each JEM identifies jets and calculates partial energy sums of missing transverse energy  $E_T^{miss}$  and total transverse energy  $\sum E_T$ . Both subsystems build Trigger Objects (TOBs) comprising location, energy, object type, XE, XS, and TE. They are sent at 160 MHz over the backplane of the crate to 12 Common Merger Extended Modules (CMXs), 8 for the CP subsystem and 4 for the JEP subsystem. The CMXs merge the TOBs of the two subsystems and route them optically to the L1 Topological Processor (L1Topo). Additionally, they send object counts to the L1 Central Trigger Processor (L1CTP). The L1Topo combines these TOBs with the ones of the L1Muon in order to make trigger decisions based on the full event topology. Its resulting decision bits are sent to the L1CTP. On a L1 Accept (L1A), that is the L1CTP considered events to be of interest, all modules of the subsystems are read-out via Read-Out Drivers (RODs). They collect all read-out data plus RoIs, manage data buffering and flow control, and build event packets to be sent to the HLT and Data Acquisition (DAQ) system.

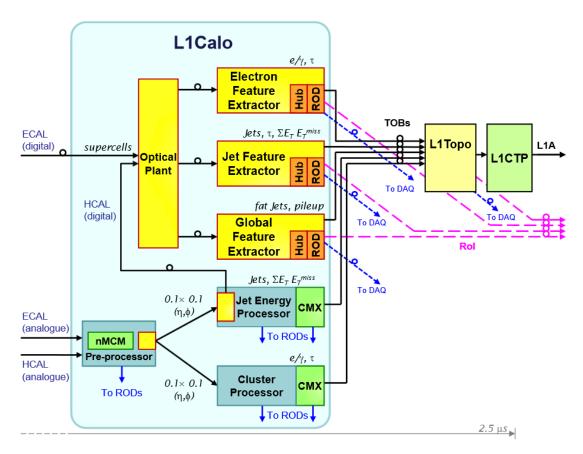

#### 2.2.4 Calorimeter Trigger Upgrade

The L1Calo system will be upgraded in the LS2 between Run 2 and 3 as part of the Phase-1 upgrade [4, 6]. According to table 2.1, the LHC will further increase its luminosity resulting in an increased number of interactions per bunch-crossing for Run 3. This will require more discriminatory power to maintain trigger efficiency. Thus, a new set of Feature Extractor (FEX) subsystems will be installed, processing calorimeter data of finer granularity with larger-area algorithms. It allows to select events more precisely, reject more background, and cover larger jets than with the JEP subsystem. Due to the increased number of interactions, improved pile-up corrections will be implemented as well. The architecture of the L1Calo system to be used during Run 3, that is after the Phase-1 upgrade, is shown in figure 2.4.

Figure 2.4: L1Calo System Architecture during Run 3 [6, modified]

The FEX subsystems are the electromagnetic Feature Extractor (eFEX) of 24 modules, the jet Feature Extractor (jFEX) of 7 modules, and the global Feature Extractor (gFEX) of a single module. The eFEX and jFEX will replace the CP and JEP, respectively while the gFEX will identify features requiring the whole calorimeter data. The FEX subsystems will operate in parallel with the CP and JEP subsystems until their outputs will have been validated. To meet the requirements of higher throughput rates due to data of finer granularity, the ECAL will provide signals over optical fibers, digitized and duplicated for each FEX module by a new on-detector Digital Processing System (DPS). In contrast, the HCAL signals will be digitized by the PPMs and duplicated by a new daughter module of the JEMs. The optical fibers will be routed to an optical plant in order to map them in such a way that each eFEX and jFEX module is fed with data partially overlapping with the data of neighboring modules. This inter-module redundancy is required by their algorithms, processing the data in moving intervals of two dimensions, so-called sliding windows. In contrast, the single module of the gFEX subsystem is fed with the whole calorimeter data.

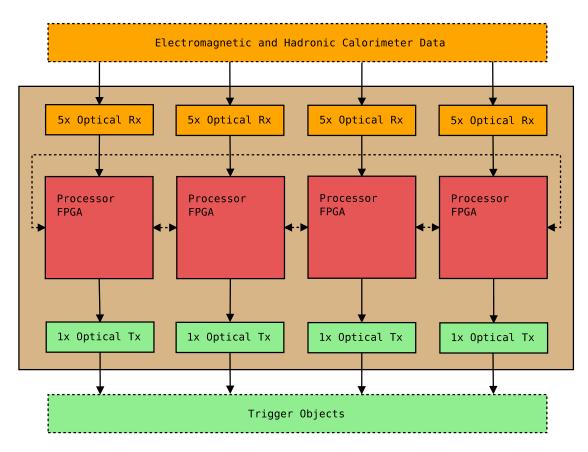

#### 2.3 Jet Feature Extractor

As part of the ATLAS calorimeter trigger upgrade of section 2.2.4, the jFEX subsystem [6] will identify in real-time large energy deposits and calculate missing transverse energies  $E_T^{miss}$  and total transverse energies  $\sum E_T$  with the data received from the electromagnetic and hadronic calorimeters. These energy deposits are indicative of jets and  $\tau$  particles. The jFEX subsystem comprises 7 jFEX modules. Each will run multiple versions of the sliding window algorithm in parallel on its four processor FPGAs in order to identify the energy deposits from the calorimeter data, as described in its specification draft [6]. They will be installed in a crate and connected through its backplane. The simplified real-time data path of the jFEX is shown in figure 2.5. The optical plant routes the data of the ECAL and HCAL to the jFEX subsystem. Each jFEX module has 5 optical receiver modules per processor FPGA. Each receiver module has 12 optical channels, summing up to 240 optical input fibers in total per jFEX module. The optical receiver modules are routed to high-performance Multi-Gigabit Transceivers (MGTs) of the processor FPGAs. These MGTs will operate at transfer rates of up to 12.8 Gbit/s, while lower rates of 11.2 Gbit/s and 9.6 Gbit/s will be considered as well [8].

Figure 2.5: Real-Time Data Path of the jFEX

Furthermore, the MGTs are capable of simultaneously looping incoming data back [9]. The resulting duplicated data is routed to neighboring processor FPGAs forming a shared data ring between them as visualized by the dotted arrows in figure 2.5. This intra-module redundancy complements the inter-module redundancy used by some versions of the sliding window algorithm. The resulting TOBs of the processed data are transferred to the L1Topo. Since this will take less bandwidth, only a single optical transmitter module per processor FPGA is required, summing up to 48 optical output fibers per jFEX module. Additionally, each jFEX module provides the read-out connectivity to the RODs via MGTs through the backplane. Furthermore, a daughter module, here referred to as mezzanine card, provides a central control interface through the backplane in order to control the jFEX and all its subcomponents like a clock generator, the optical transceivers, and several power modules.

CHAPTER 2. INTRODUCTION

## **Chapter 3**

### Hardware Design

The module control of the jFEX of section §2.3 is implemented by a daughter module, a so-called mezzanine card. Its hardware design has been done in collaboration with Reinhold Degele who did the schematics, component placement, wire routing, and soldering supervised by Dr. Ulrich Schäfer. I did the conceptual design while complying to the given design specification, chose and ordered the electrical components including a further daughter module, designed its power sequencing, and created a net list to interface it.

### **3.1 Design Specification**

Besides having algorithms running on processor FPGAs<sup>1</sup> of the jFEX to make time critical trigger decisions based on calorimeter data received over the real-time data path, other tasks and subcomponents have to be controlled and monitored as well. This is done by a central control FPGA. For reasons of flexibility this control FPGA is placed on a mezzanine card pluggable to the jFEX main board. Firstly, these algorithms must be programmed to the processor FPGAs at each power cycling. The implementation of an algorithm is stored in a so-called bit stream file. The expected file sizes are about 80 MB per processor FPGA, summing up to roughly 320 MB in total for all four FPGAs. Thus, a local storage which can be kept up to date by remote updates seems appropriate. To program an FPGA, such a bit stream file must be

<sup>&</sup>lt;sup>1</sup> Processor FPGAs are of either UltraScale VU190 or UltraScale+ XCVU9P from Xilinx [10].

transferred over a dedicated parallel bus. In order to not wait a quarter of an hour or more to power cycle the jFEX, the final transfer rate of loading the bit stream files from the internal storage and copying them over to the FPGAs should be several MB/s. It is also desired to monitor the operational states of the algorithms and to tweak their behavior by adjusting some parameters at run time. This requires additional connectivity to all processor FPGAs. For this and especially for the realtime data path, high-performance Multi-Gigabit Transceivers (MGTs) of the FPGAs are used to meet the required transfer rates of up to  $12.8 \,\mathrm{Gbit/s}$ . For such high transfer rates over long distances, optical fibers are used instead of electrical wires for external communication by routing the MGTs to optical transceiver modules. These modules can be controlled by the  $I^2C$  bus [11]. Since the incoming amount of data is higher then processed output data, transfer rate requirements for receivers and transmitters are not necessarily equal. The ATLAS TDAQ system [4] requires communication to be synchronous. Therefore, an I<sup>2</sup>C-programmable clock generator is used to derive synchronous clocks of different frequencies from a global input clock. In addition, this clock generator is capable of reducing possible jitter<sup>2</sup> of the input clock. Furthermore, the I<sup>2</sup>C bus is used to monitor various supply voltages of the power modules.

#### 3.1.1 Central Control Interface

Due to its ubiquitous nature and therefore proven reliability and availability, Ethernet was chosen for the central control interface. Commonly used communication protocols are the Transmission Control Protocol (TCP) [12] and the User Datagram Protocol (UDP) [13]. While former guaranties in-order packet delivery by detecting packet losses and managing retransmissions itself, its implementation for an FPGA would be of a more complex state machine compared with latter protocol combined with sequential packet IDs for dropped packet recovery. Hence, an UDP based implementation called IPBus [14] was developed by the Bristol University and the Imperial College London, originally for the Triggering and Data Acquisition System (TriDAS) of the CMS experiment. It was agreed to be the standard communication protocol for controlling FPGA based hardware within the ATLAS TDAQ system [4].

$<sup>^2</sup>$  Jitter is an undesired deviation in periodicity of communication signals.

#### 3.1.2 Intra-Board Communication

For controlling and monitoring the processor FPGAs, their built-in Multi-Gigabit Transceivers (MGTs) are used, allowing high transfer rates by using only six wires to each processor FPGA. Using differential signaling<sup>3</sup>, one differential pair serves as clock while two further pairs allow full-duplex<sup>4</sup> serial communication.

In order to control and monitor several ICs<sup>5</sup> of the jFEX like the clock generator, the optical transceivers, and the power modules, the Inter-Integrated Circuit (I<sup>2</sup>C) bus is used. It is a serial bus of two wires labeled SDA and SCL. Former transmits data synchronously to a clock of latter. It follows a master/slave model. Thus, a chain of ICs can be connected to the same two wires. Both wires are open-drain, that is they can only be driven low or left open. In latter case, resistors pull the wires high. Low and high are interpreted as logical "0" and logical "1", respectively. A master starts a transaction to either read from or write to a slave, referred to as master read (MR) and master write (MW) mode. A slave serves these requests by writing or reading the data, referred to as slave write (SW) and slave read (SR) mode. A transaction is composed of an address byte and one or more data bytes transferred with the most significant bit (MSB) first, each followed by an acknowledge bit, "0" for acknowledging and "1" for not acknowledging. A byte is of 8 bits. The address byte contains a 7-bit slave address followed by a direction bit, "0" for writing to and "1" for reading from a slave. When a slave detects its address, it is free to ignore a master request by not acknowledging the address byte, causing the master to abort the transaction. In MR mode the master acknowledges a byte to request the slave to write another one. Thus, each byte except the last is acknowledged. In contrast, in SR mode the slave acknowledges a byte to signify the master being able to read another one. Thus, each byte is acknowledged, but only in exceptional cases like a full data buffer a byte is not acknowledged, causing the master to abort the transaction. Additionally, one or more transactions are encapsulated by a frame of start and stop conditions while a repeated start condition separates multiple transactions within a frame. This allows multiple masters connected to the same bus by ensuring a master cannot start a transaction within a sequence of transactions of another master. A start condition is issued by firstly pulling the SDA wire low and then pulling the

<sup>&</sup>lt;sup>3</sup> Differential signaling uses two electrically complementary signals.

<sup>&</sup>lt;sup>4</sup> A full-duplex communication allows data transfer in both directions simultaneously.

<sup>&</sup>lt;sup>5</sup> An integrated circuit (IC) is composed of electronic circuits on a compact chip.

SCL wire low while a stop condition is issued by firstly releasing the SDA wire and then releasing the SCL wire. Various speed modes are defined, among others, with standard mode of 100 kbit/s and fast mode of 400 kbit/s.

#### **3.1.3 Debugging Facilities**

A universal asynchronous receiver/transmitter (UART) is a hardware module for serial communication commonly included in microcontrollers<sup>6</sup> and CPUs. Due to its simplicity it suits well for early stage debugging like a boot process of a CPU. A configurable number of data bits can be sent, usually eight bits, but five to nine bits are possible as well. If not nine bits are chosen, an optional parity bit<sup>7</sup> can be appended giving a chance of error detection. These data bits along with an optional parity bit are encapsulated by a start bit of value "0" and one or two stop bits of value "1". A value of "0" or "1" is represented by a low or high signal, respectively. Thus, when idle, the signal is kept high to be able to detect a start bit. The frame of start and stop bits is required for synchronization since there is no clock signal. A voltage level translator [15] fulfills the electrical characteristics defined by the Recommended Standard 232 (RS-232) for serial communication commonly used for serial ports of computers. Alternatively, the Universal Serial Bus (USB) can be interfaced with the help of an onboard USB-to-UART bridge [16].

### **3.2 Conceptual Design**

An FPGA allows customizable, true parallel, and accurately timed digital signal processing (DSP), making it a first-choice core component of hardware designs with focus on time critical signaling and long-term use. But tasks of less time accuracy like accessing an SD card<sup>8</sup> or processing data on a higher level to control modules like a clock generator are well suited to a CPU running an operating system with a whole ecosystem of applications and libraries. To use advantages of both worlds, a CPU and an FPGA, communication between them is required to delegate tasks or share data. Instead of using separate chips for CPU and FPGA with externally

<sup>&</sup>lt;sup>6</sup> A microcontroller is a compact computer with I/O peripherals on a single IC.

<sup>&</sup>lt;sup>7</sup> A parity bit indicates whether the number of data bits with value "1" is even or odd.

<sup>&</sup>lt;sup>8</sup> A Secure Digital (SD) card is an exchangeable non-volatile data storage device.

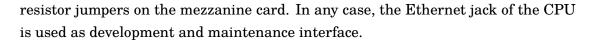

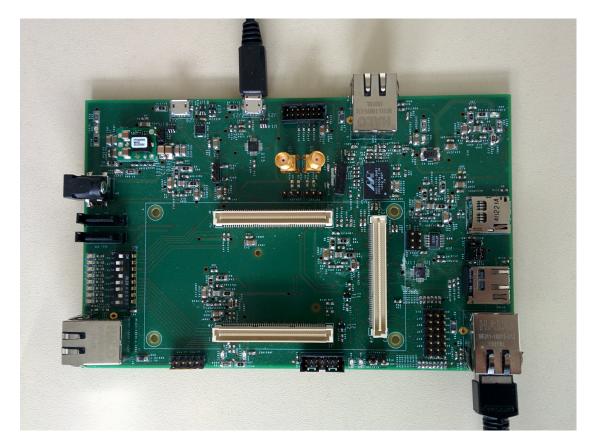

hardwired connectivity, a more flexible alternative was chosen, a hybrid system on a chip (SoC), combining an FPGA and a CPU inside a single chip with many customizable interconnects in between. In regard to a short development time, the first iteration of the mezzanine card does not populate this hybrid SoC on its own, instead it is interfaced through a daughter system on a module (SoM) from Avnet called PicoZed 7Z030 [17] based on a hybrid SoC from Xilinx called Zynq XC7Z030 [18]. The PicoZed is plugged onto the mezzanine card, already fulfilling the electrical requirements of the Zynq. In figure 3.1 the block diagram of the mezzanine card is shown. The brown, dark green, and light green boxes represent a simplified jFEX main board, mezzanine card, and PicoZed daughter module, respectively while each is plugged onto the other. The purple box within the light green one represents the Zynq with its CPU in blue and its FPGA in red, referred to as processing system (PS) and programmable logic (PL), respectively. Components are colored blue or red whether they are chained with the CPU or the FPGA, respectively while components being chained with both or being connectible to both are colored purple like the Zynq.

Though the first iteration of the *jFEX* will have wire routings for all four processor FPGAs, it will be populated with only two of them to firstly gain experience with initial tests. Thus, only connectivity for two processor FPGAs is required for the first iteration of the mezzanine card. The PicoZed series was chosen over another SoM series from Avnet called MicroZed [19], since that series does not provide MGTs, which are required to control and monitor the processor FPGAs. Two of four available MGTs of the PicoZed are reserved for the processor FPGAs while a third one is connected to a PHY<sup>9</sup> for Ethernet communication via FPGA. This PHY is populated on the mezzanine card and exposed by an Ethernet jack also known as RJ45 connector. Another Ethernet jack is connected to a PHY of the PicoZed allowing Ethernet communication via CPU. This whole setup is supposed to be installed in a crate of multiple devices being interfaced through the crate backplane (BP). Among other connectivity, this backplane is connected through the jFEX to a third Ethernet jack in purple of the mezzanine card. Its purpose is to be either connected to the Ethernet jack of the FPGA in red or to the Ethernet jack of the CPU in blue. In this way, as a precautionary measure regarding possible future changes to the central control interface of section 3.1.1, it is possible to choose between FPGA based or CPU based control through the backplane by using an Ethernet cable instead of multiple  $0 \Omega$

<sup>&</sup>lt;sup>9</sup> A physical layer device (PHY) implements the physical layer of a communication protocol.

Figure 3.1: Block Diagram of the Mezzanine Card

Though the mezzanine card is supposed to be plugged onto the jFEX, it can operate without it as well, allowing standalone tests. Thus, it is powered by either the jFEX or an external power supply connected to its power jack. Both 12 V supply voltages, the one of the jFEX and the one of the external power supply, are connected to a chain of further power supplies [20] of the mezzanine card represented by the light green box in figure 3.1, each regulating a different supply voltage. Two diodes protect the 12 V power supplies from each other in case both are connected at the same time. Each power supply of the chain can be enabled by raising its input pin labeled "EN". It will indicate when its power is good (PG), that is its voltage has stabilized, by raising an output pin labeled "PG". When power cycling the mezzanine card, the

PicoZed is permanently supplied with 5 V. But supplying its banks<sup>10</sup> is required to be delayed until the internally regulated supply voltages of the PicoZed have stabilized. Furthermore, it is advised to supply MGT voltages in a sequence from low to high voltages to reduce current drawn during power up [21]. As visualized in figure 3.1, the PicoZed exposes a signal labeled "Free", indicating when the mezzanine card is free, in a sense of being allowed, to supply the banks. This signal is connected to the input pin "EN" of the first power supply of the chain, enabling one power supply after another by cascading the output pins "PG" of each power supply to the input pin "EN" of the next power supply in the sequence they are supposed to power up. The output pin "PG" of the last power supply of the chain is connected to the signal of the PicoZed labeled "Good" to finally enable the Zynq after all supply voltages have been stabilized, which are 1.0 V for MGT transceivers, 1.2 V for MGT termination circuits, 1.8 V for high-performance banks<sup>11</sup>, 2.5 V for the PHY of the mezzanine card, and 3.3 V for high-range banks<sup>12</sup> in the order mentioned.

The Zynq boots from one of two SD cards via an SDIO port expander [22] serving as voltage level translator as well. The SD card is selected by two jumpers, the second SD card serves as fallback system. Since the PicoZed provides an USB On-The-Go (OTG) interface, an appropriate micro-AB USB plug was populated on the mezzanine card. The two UART modules of the Zynq are connected to a RS-232 voltage level translator, each exposed by a header<sup>13</sup> of three pins, two for receiver (Rx) and transmitter (Tx) plus one for ground (GND). Additionally, one of these UART modules can be connected to a USB-to-UART bridge via 0  $\Omega$  resistor jumpers, exposed by an micro-B USB plug. As further debugging facilities, an array of eight switches and an array of eight LEDs, connected to the FPGA, can be used as quick configuration and status indicator, respectively.

All connectivity of the header connector<sup>14</sup> to the jFEX is additionally exposed on separate headers and connectors to allow standalone tests of the mezzanine card. Two I<sup>2</sup>C modules of the CPU and eight I<sup>2</sup>C modules possibly implemented by the FPGA are exposed by an array of headers of three pins each, two for SDA and SCL plus one for GND. Each of the two MGTs for the processor FPGAs can be accessed

<sup>&</sup>lt;sup>10</sup> A bank of an FPGA is a group of I/O pins sharing common resources like a supply voltage.

<sup>&</sup>lt;sup>11</sup> The PicoZed exposes 100 high-performance (HP) [23] user PL I/O pins.

<sup>&</sup>lt;sup>12</sup> The PicoZed exposes 35 high-range (HR) [23] user PL I/O pins.

<sup>&</sup>lt;sup>13</sup> A pin header or simply header is of one or more rows of pins.

<sup>&</sup>lt;sup>14</sup> A header connector is meant to be plugged onto a header.

by a SATA<sup>15</sup> connector when configuring their  $0 \Omega$  resistor jumpers appropriately, allowing a loop back test with a crossover SATA cable. The differential MGT reference clock is available by two SMA connectors<sup>16</sup>. The JTAG<sup>17</sup> debug interface of the Zynq, cascaded with the processor FPGAs of the jFEX to be part of a boundary scan, is exposed by a separate header as well.

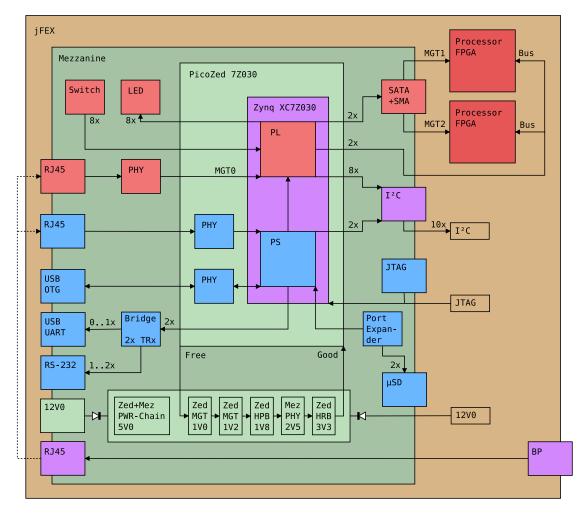

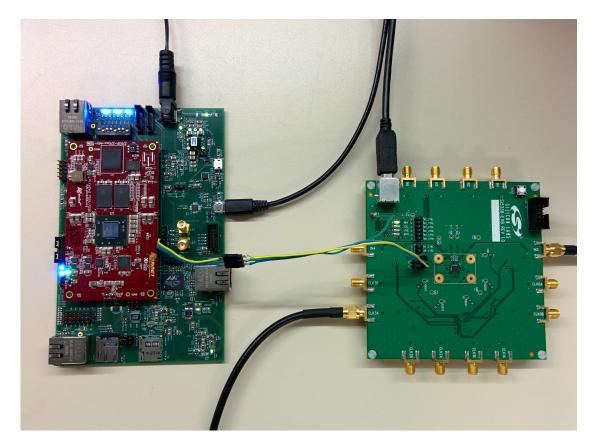

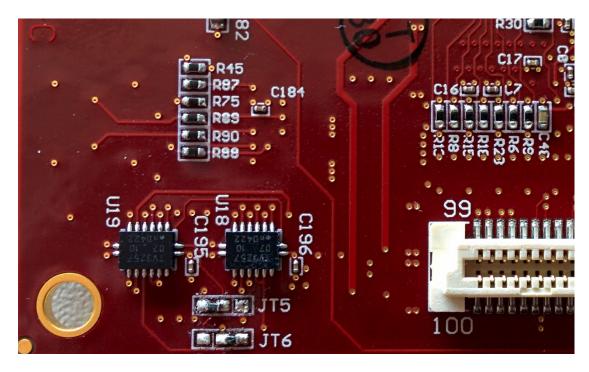

### **3.3 First Iteration**

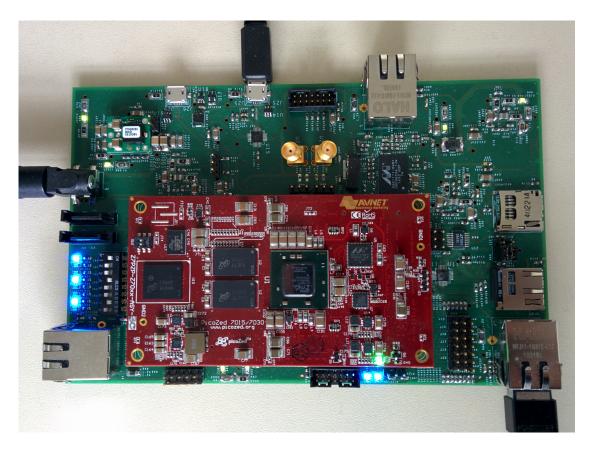

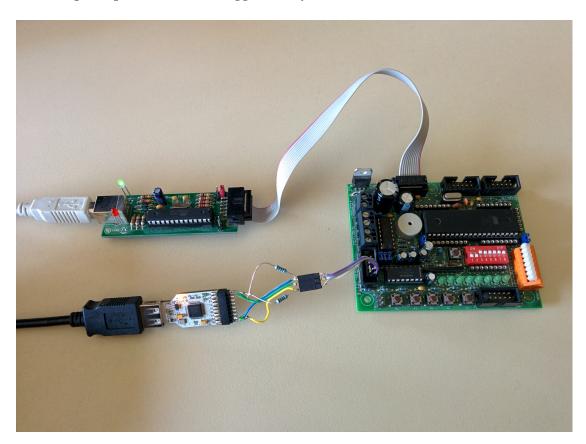

The first iteration of the mezzanine card is shown in figure 3.2. Its two SD card slots are on the right above the Ethernet jack of the CPU. On the left of this jack are seven of the eight I<sup>2</sup>C headers of the FPGA. The eighth one was placed more to the left near the JTAG header. The two I<sup>2</sup>C headers of the CPU are below the two golden SMA connectors for the differential MGT reference clock. The SATA connectors of the two MGTs are on the left below the power jack and above the switch and LED arrays. The Ethernet jack of the backplane is on the left bottom. The USB cable on the top is connected to the USB-to-UART bridge with the USB OTG plug on its left and the Ethernet jack of the FPGA on its right. The PicoZed can be plugged onto the three white headers.

<sup>&</sup>lt;sup>15</sup> Serial AT Attachment (SATA) [24] is a computer bus interfacing mass storage devices.

<sup>&</sup>lt;sup>16</sup> SubMiniature version A (SMA) connectors are commonly used for coaxial cables.

<sup>&</sup>lt;sup>17</sup> The Joint Test Action Group (JTAG) [25] interface allows testing of IC interconnects.

Figure 3.2: Mezzanine Card

At the time of finishing the hardware design of the mezzanine card, the pin layout of the header of the jFEX, to connect the mezzanine card onto, was not yet finalized. To not postpone the production and debugging of the mezzanine card, it was decided to drop its header connector, but for the first iteration only.

## **Chapter 4**

## **Software Development**

In order to test, control, and advance the mezzanine card of section §3.3, several software packages have been developed for long-term use including a workflow kit named Zed Tool (z21), a helper tool polling for pluggable devices named plug, a file transfer application between CPU and FPGA named Feedback Synchronized I/O (fsio), and a controller of the clock generator named si53xx. These software packages including their sources are provided on a compact disk (CD) attached to this thesis. Additionally, each software package is hosted on a web server at following addresses:

https://qulx.org/z2l

https://qulx.org/plug

https://qulx.org/fsio

https://qulx.org/si53xx

They have been developed with focus on reusability and extendibility in mind by structuring their source code hierarchically from abstract interfaces down to concrete implementations while not sacrificing performance to allow flexible and extensible use cases. Finally, libraries are served with general-purpose applications to ease use of them while these applications and libraries along with manual pages and quick introductions are distributed in a package format allowing automated configuration and compilation with the help of the GNU Build System also known as the Autotools [26]. Compact algorithms and interfaces, only parts of the source code with a so-called high expressiveness, are shown, allowing their motivational description to reason and explain the conceptional choices of the software design in a whole, being an essential part of this thesis, and to finally serve as documentation for further development. Software was developed with Debian Jessie (amd64<sup>1</sup>) [27] as operating system and was additionally tested with PetaLinux 2015.4 (arm-linux-gnueabi<sup>2</sup>) [28] from Xilinx, an embedded operating system running on the mezzanine card.

### 4.1 Workflow Kit

Development for the hybrid SoC Zynq is composed of three major processes. The configuration of an FPGA is represented by a bit stream file described by a hardware abstraction language (HDL). This bit stream file can be generated by the Vivado Design Suite [29] from Xilinx. The CPU runs an embedded operating system called PetaLinux. It can be customized and compiled with the PetaLinux Tools from Xilinx. On top of this operating system, user application software is installed. These applications are cross-compiled with the help of the GNU Build System also known as the Autotools. All these three toolchains, the Vivado Design Suite, the PetaLinux Tools, and the Autotools store their configurations, source files, and destination files in their own project folders. While cross-compiling application software is almost independent from configurations of the other two projects, the PetaLinux Tools require configurations to be imported from the Vivado Design Suite project in order to appropriately customize the operating system. To manage all three projects and automate their integration into each other to speed up the development process, the software package Zed Tool (z21) has been developed.

#### 4.1.1 Dependency Resolution

Zed Tool combines all three projects into a single higher-level project. It resolves dependencies between the three toolchains by automatically invoking them to generate their destination files from their source files, like the bit stream from the HDL sources, a boot image and a root file system image of the operating system from its source code and configuration files, and the application binaries from their source code files. Such automation is possible thanks to Vivado being based on a scripting

<sup>&</sup>lt;sup>1</sup> The AMD64 port supports the 64-bit version of the x86 instruction set.

<sup>&</sup>lt;sup>2</sup> The arm-linux-gnueabi cross-compiler target without hard-float support is used.

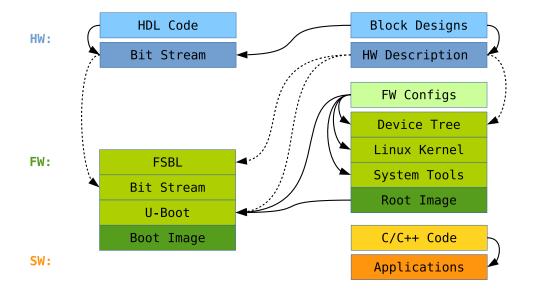

language called Tool Command Language (TCL) [30] allowing it to be invoked without its graphical user interface (GUI). The three projects along with their toolchains, Vivado Design Suite, PetaLinux Tools, and Autotools are referred to as hardware (HW), firmware (FW), and software (SW) projects, respectively. Their own dependencies between destination and source files and their inter-project dependencies are visualized in figure 4.1. Zed Tool automatically resolves these dependencies by comparing timestamps of destination files with the ones of their source files. When a destination file is older than one of its source files, it will be regenerated by invoking its appropriate tool. A common tool for resolving such file dependencies is called GNU Make [31]. The dependencies are described by a so-called Makefile which is parsed by this tool. Alternatively, a self-executable Makefile automatically invokes Make when it will be executed, which is the case for Zed Tool. The three dependency stages, HW in blue, FW in green, and SW in orange of figure 4.1 are represented by their destination files in dark blue, dark green, and dark orange, respectively while their sources are lightly colored. The normal green colored components compose the dark green ones, indicated by having no gap between them. Continuous arrows are intra-project dependencies while dashed arrows are inter-project dependencies, these are destinations being sources of other projects. While the SW stage is simply represented by application binaries without inter-project dependencies, the HW stage is made up of two destination files, a bit stream file and a hardware description file, not to be confused with the HDL files. Both are sources of the FW stage.

Figure 4.1: Dependency Graph

While the bit stream depends on both HDL and block design files, the hardware description file is independent of HDL files. Block designs can describe interconnects between CPU and FPGA and are used to configure hardware interfaces like I<sup>2</sup>C or UART modules. They are made up of Intellectual Property Cores (IP Cores) which can be instantiated by selecting them from the Vivado IP Catalog. A remarkable property of this dependency graph is that there is no single dependency from left to right, arrows only point from right to left. Thus, when only HDL files change, it is not necessary to invoke the tools for regenerating the root image, which would actually invoke a lot of other internal Makefiles of the PetaLinux Tools to recheck all destinations for their possibly updated sources, which are the first stage boot loader (FSBL) [32], the Universal Boot Loader (U-Boot) [33] also known as "Das U-Boot", the device tree [34], the Linux kernel [35], and all the system tools included in the root file system, which requires time. The FSBL and the U-Boot are actually components of the boot image but they are generated by the root image generation process and just copied over when generating the boot image. The FSBL in conjunction with the U-Boot make up a two stage boot loader to load the kernel which parses the device tree providing information about available hardware and their configurations. Finally, the kernel mounts the root file system and starts several system services. The problem is, when Vivado is invoked to regenerate the bit stream due to changed HDL files, it additionally regenerates the hardware description file though no block design files have changed. This would unnecessarily trigger the regeneration of the root image. To prevent this, the hardware description file is duplicated by Zed Tool but only when block design files have changed. This duplicate is used as HW destination instead of the original one which is unnecessarily regenerated each time HDL files have changed. In this way, the development process is speed up by saving the time of the root image generation process each time HDL files but no block design files have changed. After regenerating the bit stream due to changed HDL files, only the boot image generation process is triggered which is of almost no time compared with the root image generation process.

#### 4.1.2 Modification Management

Besides improvements regarding development time by focusing on the sources themselves instead of remembering how and when to regenerate their destinations, another goal of Zed Tool is to make image generation reproducible which is indispensable for long-term use and maintenance. It allows to distribute the higher-level project as source files only, being lightweight compared with the final size of a whole operating system. The Vivado Design Suite already allows separation of source and

destination folders while the Autotools have routines to clean up the project folder from its destination files. Though the PetaLinux Tools have similar clean up routines, there are still a lot of generic files left. Thus, Zed Tool manages saving, loading, editing, and diffing<sup>3</sup> of essential configuration files of PetaLinux and its various subsystems, which are the FSBL, the U-Boot, the device tree, the Linux kernel, and the system tools to be included in the root file system. Since Zed Tool is a self-executable Makefile, it accepts only targets, besides options for Make itself, as command line arguments, which are nothing else than destination files or aliases of destination files. It is also possible to define so-called phony targets not being related to a file in order to implement commands. Zed Tool provides a GNU Bash<sup>4</sup> completion script as well. When writing z21 in a terminal prompt followed by double pressing TAB, the terminal will suggest all available alias targets for Zed Tool, as shown in figure 4.2. The five targets fw.edit.plt, fw.edit.ubl, fw.edit.dts, fw.edit.lnx, fw.edit.rfs allow editing the FSBL, the U-Boot, the device tree, the Linux kernel, and the system tools to be included in the root file system, respectively while fw.edit.sys allows to edit the configuration of PetaLinux itself and fw.edit invokes all previously mentioned targets one after the other. Changes made, are directly stored in the project folder of the PetaLinux Tools. After confirming their functionality by testing these modifications, they can be saved to a separate PetaLinux source folder created by Zed Tool by invoking fw.save. In case these modifications caused more problems instead of reducing them, they can be revoked by loading the previous configurations of the source folder with fw.load. When a lot of modifications have been done at once, the target fw.diff gives an overview of them by only printing the differences of configurations in the destination folder compared with the ones in the source folder, allowing to confirm them before possibly saving them with fw. save. In contrast, HW modifications can be done by launching Vivado with its GUI and letting it automatically open the HW project by invoking the target hw.edit.

<sup>&</sup>lt;sup>3</sup> Comparing two files with a common tool called diff [36].

<sup>&</sup>lt;sup>4</sup> GNU Bash [37] is the default Unix shell of Debian for interactive terminals.

| Terminal                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                    |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| File Edit View Search                                                                                                                                                                                                                                  | Terminal Help                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                    |  |  |

| n3vu0r@wetap149:~/Pro<br>all<br>clean<br>distclean<br>dry-pull<br>dry-push<br>fw<br>fw.clean<br>fw.diff<br>fw.distclean<br>fw.edit<br>fw.edit.dts<br>fw.edit.lnx<br>fw.edit.lnx<br>fw.edit.plt<br>fw.edit.rfs<br>fw.edit.sys<br>fw.edit.ubl<br>fw.load | Terminal Help<br>jects/jfex-modctl\$ z2l<br>fw.save<br>hw<br>hw.clean<br>hw.distclean<br>hw.edit<br>poweroff<br>pull<br>push<br>reboot<br>sftp<br>ssh<br>sw<br>sw.clean.fsio<br>sw.clean.fsio<br>sw.clean.rsync<br>sw.clean.si53xx<br>jects/jfex-modctl\$ z2l | sw.clean.xxd<br>sw.clean.zelsius<br>sw.distclean<br>sw.distclean.fsio<br>sw.distclean.pugixml<br>sw.distclean.rsync<br>sw.distclean.si53xx<br>sw.distclean.xxd<br>sw.distclean.zelsius<br>sw.fsio<br>sw.pugixml<br>sw.rsync<br>sw.si53xx<br>sw.xxd<br>sw.zelsius<br>tty<br>zelsius |  |  |

| fw.load                                                                                                                                                                                                                                                | sw.clean.si5́3xx                                                                                                                                                                                                                                              | zelsius                                                                                                                                                                                                                                                                            |  |  |

|                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                    |  |  |

Figure 4.2: Usage of Zed Tool

#### 4.1.3 Development Process

To actually test modifications, not only those to PetaLinux configurations but also modifications to HW or SW projects, the appropriate modified destination files have to be transferred to the target device, the mezzanine card. What can cause a lot of trouble is when modifications have been done but some modified destination files have been forgotten to be transferred. This gives the impression that these modifications either have no effect since they have actually not been applied or break the system since they have actually been applied only partially. Zed Tool keeps track of all modified destination files with the help of a common tool called rsync [38]. It allows local or remote updates by synchronizing a destination folder regarding its source folder by a technique called rolling checksum. Additionally, it provides a socalled dry-run mode simulating a synchronization to confirm nothing unintended will accidentally happen. Thus, to automatically transfer all modified destination files or to only simulate it, the targets push or dry-push are used, respectively. For doing the opposite, that is making a backup of the target device, the targets pull and dry-pull are available. In case the bit stream was modified, a reboot is required to reprogram the FPGA, which can be triggered with the reboot target. In order to

monitor the boot process, an UART or an UART over USB terminal connection can be establish with a common terminal emulator called picocom by invoking the tty target. After the device has booted, a more reliable TCP terminal connection can be established with the help of a common tool called Secure Shell (SSH) [39] by invoking the ssh target. All this can be done at once by passing these targets to Zed Tool from left to right in the order they should be invoked with a command line prompt of z21 push reboot tty ssh. There is one problem, after triggering a reboot, the UART device vanishes causing the tty target to fail. To solve this, a helper script was written polling for the UART device until it is available again. Due to its general-purpose usability this script is separately distributed as the software package plug. When the boot process has finished, the terminal can be exited by pressing CTRL+A+X. Afterwards, the SSH terminal is established for testing the modified applications. Besides synchronization of the whole destination folder, partial transfers can be done with the sftp target as well, making use of the SSH File Transfer Protocol. On-thefly modifications of configuration files at the target device are also possible over this protocol. Thanks to the default file browser of Debian called Nautilus, these remote files can transparently be accessed like local files. The destination files of the three dependency stages HW, FW, and SW have corresponding alias targets hw, fw, and sw, respectively. First one is practical to test if modifications to HDL and block design files are valid without triggering the regeneration of the root image when the intention is to continue modifying these HW sources. The targets sw.PKG, sw.clean.PKG, and sw.distclean.PKG behave similarly to the standard Make targets all, clean, and distclean of the software package labeled "PKG", respectively. The targets sw, sw.clean, and sw.distclean invoke the corresponding targets of all available software packages. The first of these, sw.PKG or sw, additionally installs the software package or all software packages to the local destination folder, respectively. It can then be synchronized with the remote destination folder. Another helper script, invoked with target zelsius but in contrast to plug being distributed with z21, reads out the raw temperature data of the Zynq analog-to-digital converter (XADC) and prints the calculated SoC temperature in millidegree Celsius on the screen.

## 4.1.4 Toolchain Encapsulation

Further handy features of Zed Tool are encapsulating environment settings, required to be loaded before the Vivado Design Suite and the PetaLinux Tools can be executed, and to serve the addresses of license servers and paths to license files, required for certain features or IP Cores of the Vivado Design Suite. This encapsulation is necessary, since otherwise these settings would break functionality of other tools. For instance, the order in which library paths are scanned is changed to make PetaLinux Tools work, but causes subsequent invocations of other tools to fail. Thus, for each executable, Zed Tool installs a so-called wrapper script launching a sub-process and changing only the environment of this sub-process, which then invokes the corresponding executable. When terminated, the sub-process will be terminated as well, but the environment settings of the main process, the actual terminal, were not being touched.

# 4.2 CPU/FPGA Communication

In order to use the advantages of both a CPU and an FPGA, communication between them is required to delegate tasks or share data. The so-called physical address space of the CPU has a reserved address range to access dedicated registers of the FPGA. Since the CPU runs an operating system whose kernel uses a memory management technique called virtual memory [40], only kernel modules have direct access to the physical memory while application software must map physical addresses to their virtual address space. This mapping is done by the system call<sup>5</sup> mmap [41]. It takes a physical address as argument and returns an appropriate virtual address used by the software application. When accessing the virtual address, it is translated to the physical address and its data might be cached by the kernel, resulting in a possibly delayed, so-called indirect memory access. Thus, there are two ways of establishing a communication channel, developing either a kernel module or an application software library managing the memory mapping. While a kernel module might promise higher transfer rates and less latency due to its direct memory access (DMA), interfacing the DMA API<sup>6</sup> [42] of the kernel is a more complex task requiring more parameters to be studied, resulting in longer development time and increased maintenance effort in case of new kernel versions. In contrast, setting up memory mapped channels is more flexible requiring no additional parameters among the address ranges to be mapped, each specified by its base address and width. For these reasons, implementing memory mapping by an application software library was chosen. Thus, the software package fsio has been developed.

$<sup>^{5}\,\</sup>mathrm{A}$  system call allows application software to request a certain service from the kernel.

<sup>&</sup>lt;sup>6</sup> An application programming interface (API) provides routines to use a software component.

Along with its library libfsio, it contains two binaries, fsio and fsio-tvgen. Former is a file transfer application while latter is a test vector<sup>7</sup> generator.

## 4.2.1 Communication Protocol

Due to the nature of caching and clock domain crossing between CPU and FPGA, reading data from and writing data to the FPGA must be synchronized by an out-ofband<sup>8</sup> handshake<sup>9</sup> signal to avoid data corruption. For example, writing data from the CPU to the FPGA must be finished before the FPGA reads it, otherwise the data might be partially out of date. Thus, the CPU has to inform the FPGA when it is allowed to read the data by toggling a separate handshake signal after the data has been written. But just executing one write instruction after another is not enough, since caching does not guarantee to strictly preserve their order. A solution to this problem is, to continuously read the written data back on a separate mapping and compare them until they are equal, before executing another instruction. Hence the name Feedback Synchronized I/O (fsio) was chosen for this software package.

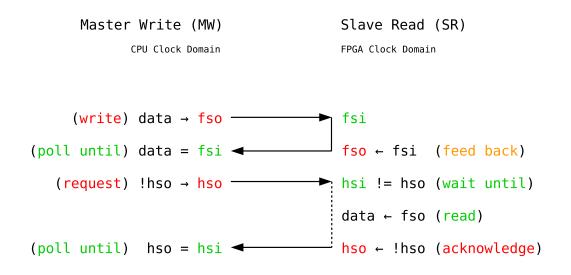

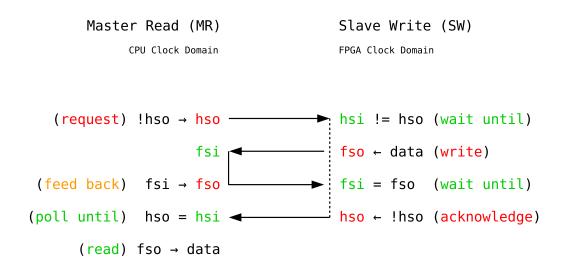

To make the communication stateless regarding the actual value of the handshake signal, a master/slave model was chosen with the CPU as master and the FPGA as slave. That means, only the CPU is allowed to toggle the handshake signal. In this way, an application does not need to remember the previous value each time it will be executed. Instead, it can just read it from the FPGA after mapping a channel without otherwise potentially missing a handshake toggle. Thus, there are four routines, master write (MW), slave read (SR), master read (MR), and slave write (SW). First two are used to write to the FPGA while last two are used to read from the FPGA, as illustrated in figure 4.3 and 4.4, respectively. In both figures, the CPU on the left and the FPGA on the right represent an unidirectional communication channel. The arrows indicate the two feedback loops of each figure, one for the data and one for the handshake. A loop has both input and output mappings, labeled "fsi" and "fso" for the data, and "hsi" and "hso" for the handshake, respectively. What is labeled as input for the CPU, is labeled as output for the FPGA, and vice versa. Time flows from top to bottom, except for the orange colored feeding which is done continuously on the FPGA and alternately with the handshake polling on the CPU.

<sup>&</sup>lt;sup>7</sup> A test vector is made up of specific input data to test a given software component.

<sup>&</sup>lt;sup>8</sup> An out-of-band signal exchanges information in a separate channel from the data stream.

<sup>&</sup>lt;sup>9</sup> A handshake allows requesting and acknowledging chunks of data between two entities.

Figure 4.3: Writing To the FPGA

The master write routine firstly writes the data, and repeatedly reads it back until they are equal. Then it toggles the handshake signal requesting the FPGA to read the data. Afterwards, the slave read routine of the FPGA acknowledges the request by feeding back the toggled handshake signal for which the CPU is waiting for by polling it.

Figure 4.4: Reading From the FPGA

In contrast, the master read routine firstly toggles the handshake signal requesting the FPGA to write data while the CPU repeatedly feeds it back. The slave write routine of the FPGA compares the written with the fed back data until they are equal. Afterwards, it acknowledges the request by feeding back the toggled handshake signal, allowing the CPU to finally read the data.

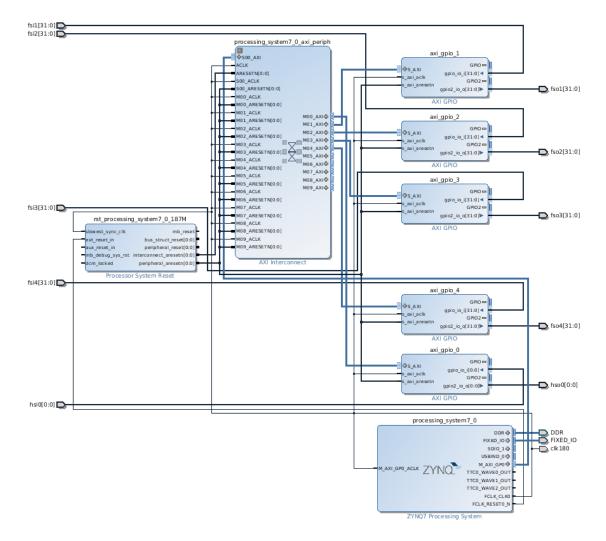

# 4.2.2 Memory Mapping

The software tool used to create FPGA designs is the Vivado Design Suite from Xilinx. Interconnects from FPGA to CPU are described by a so-called block design, as shown in figure 4.5. The block "processing\_system7\_0" represents a reduced interface of the CPU while the registers to be mapped are represented by the blocks "axi\_gpio\_0", "axi\_gpio\_1", "axi\_gpio\_2", "axi\_gpio\_3", and "axi\_gpio\_4", here referred to as AXI GPIO maps. Blocks are Intellectual Property Cores (IP Cores). They can be instantiated by selecting them from the Vivado IP Catalog. The five AXI GPIO maps are instances of the AXI GPIO IP Core<sup>10</sup>, connected to the CPU via the Advanced eXtensible Interface (AXI) of the Advanced Microcontroller Bus Architecture (AMBA). While the CPU acts as AXI master, the five maps act as AXI slaves. The block "processing\_system7\_0\_axi\_periph" between them manages memory mapped transfers of one or more masters to one or more slaves.

$<sup>^{10}</sup>$  The AXI GPIO IP Core [43] allows general-purpose I/O (GPIO) CPU/FPGA interconnectivity.

Figure 4.5: CPU/FPGA Interconnects [29]

As shown in figure 4.6, a map provides a so-called dual channel mode. This allows the first channel to be input only and the second channel to be output only. This suits the proposed protocol well since one of the two channels can be used as feedback loop reducing the number of maps to not bloat the block design.

| GPIO                    |              |                        |